|

Lundi 02 février 2026 - 11:30 |

| Translate |

|

| Rubriques |

| Réseaux sociaux |

|

| Liste des jeux Amiga |

|

| Trucs et astuces |

|

| Glossaire |

|

| Galeries |

|

| Téléchargement |

|

| Liens |

|

| Partenaires |

|

| A Propos |

|

| Contact |

|

|

|

Note : traduction par David Brunet.

Droit d'auteur et distribution

Ce projet est librement distribuable. Vous pouvez m'envoyer ce que vous voulez, juste pour me dire si cela vous a plu ou non.

L'histoire

Il y a quelques mois, j'ai réfléchi à la limite des 8 Mo de mémoire de la carte accélératrice Big Bang de Hardital pour Amiga 500 (et sa variante Super Big Bang pour A2000). J'ai trouvé cela inhabituel car la quantité maximale de mémoire adressable est généralement de 4 Mo.

J'ai jeté un coup d'oeil à la puce du contrôleur DRAM de cette carte. C'est un circuit DP8421A produit par National Semiconductor. J'ai trouvé la page Internet de National Semiconductor répertoriée dans les archives de Chip Directory. Après quelques recherches, j'ai pu mettre la main sur les fiches techniques de cette puce. La lecture de ces documents fut suffisante pour confirmer mon hypothèse. Le DP8421 peut contrôler jusqu'à 16 Mo de mémoire avec l'utilisation de puces de 1 Mo.

Je savais à présent que cette extension mémoire pouvait être réalisée, mais la question était : serait-ce facile ? Aujourd'hui, je peux répondre "oui, assez facilement", mais j'ai rencontré de nombreux problèmes au cours de son projet et de sa réalisation. En tout cas, j'ai finalisé le projet ! Et cela ne coûte pas cher !

Limites

J'ai fabriqué cette extension mémoire avec deux barrettes SIMM EDO de 8 Mo. Si vous choisissez d'utiliser des barrettes SIMM, il est impératif qu'elles soient assemblées avec des puces de 1 Mo. Actuellement, l'une de mes cartes SIMM utilise 16 puces avec une densité de 1Mbx4, l'autre utilise 4 puces avec une densité de 1Mbx16. Pour vérifier si le module SIMM est fonctionnel, vous devez vous assurer que la broche 19 n'est pas utilisée (connectée à aucune des puces du module SIMM).

J'ai dû créer un adaptateur ZIP vers SIMM pour connecter les deux barrettes SIMM sur les emplacements ZIP de la carte Big Bang. J'ai réalisé les connexions en utilisant des fils fins. Essayez de garder ces fils aussi courts que possible, car ils introduisent des bruits et des délais, entraînant des lectures et écritures erronées à partir de/vers la mémoire. Les connexions /RAS semblent être les plus délicates. Ce n'est que lorsque j'ai soudé ces fils directement sur l'emplacement du DP8421 (au lieu des bancs ZIP) que je me suis débarrassé de toutes les erreurs de lecture/écriture. C'est probablement à cause des bruits de cet adaptateur que le surcadençage de la carte à 33 MHz provoque la réapparition des erreurs de lecture/écriture en mémoire. Il y a quelque temps, j'ai repassé l'horloge de ma carte à 25 MHz, car j'ai découvert que mon processeur et mon FPU fonctionnaient à l'origine à 20 MHz, et qu'ils étaient donc déjà surcadencés à 25 MHz par Hardital lui-même.

Les 16 Mo de mémoire ne se configurent pas automatiquement. Ceci est dû à la limite de 8 Mo des Amiga 500/2000 en matière d'espace d'adresse AutoConfig. Par conséquent, vous devez ajouter de la mémoire lors du démarrage à l'aide d'une commande comme "Addmem". De plus, les 16 Mo de mémoire sont formés de deux blocs de 8 Mo chacun. Il est également possible que vous ne puissiez plus basculer vers le mode 68000, car il pourrait y avoir un conflit entre les deux barrettes SIMM, mais je n'ai pas testé car je n'ai aujourd'hui plus de raison de dégrader mon système.

J'utilise quelques portes CMOS pour cette extension. Elles introduisent un délai de l'ordre de 20 à 40 ns. J'ai également développé quelques circuits logiques alternatifs (voir chapitre annexe en fin d'article) basés sur des portes logiques ; ils peuvent être plus rapides que ma première solution si vous les fabriquez avec des puces TTL.

Réalisation théorique

Pour comprendre le fonctionnement de ma bidouille, vous devez connaître la signification de certains signaux.

| Nom | Emplacement | Description |

| /ML | Broche 52 du DP8421 ; 68030 | Lorsque ce signal est activé (low), le DP8421 entre en mode programme. Il provient du signal /RESET du 68030 |

| /RAS0,1,2,3 | Broches 38, 39, 40 et 41 du DP8421 | Ces signaux sont activés exclusivement, c'est-à-dire que si l'un est activé, les autres sont annulés. Le signal activé sélectionne sa banque de mémoire correspondante |

| B0,B1 | Broches 16 et 17 d'IC32 ; broches 32 et 33 du DP8421 | Ces signaux sont générés par la GAL IC32 et envoyés au DP8421. Lorsque /ML est activé, leurs valeurs sont utilisées pour programmer le contrôleur DRAM. Lorsque /ML est annulé, leurs valeurs sont utilisées pour générer les signaux /RAS. |

Pour fonctionner correctement, le DP8421 doit être programmé. La programmation est faite en lisant l'état de certains signaux (B0, B1...) au moment où le signal /ML est activé. Normalement, le composant IC32 (une puce programmable personnalisée) gère les valeurs B0 et B1 en mode normal et en mode programme. Lorsque /ML est activé, les valeurs correctes sont envoyées au DP8421 pour le programmer. Lorsque /ML est annulé, le signal B1 est toujours égal à 0 et seul B0 est utilisé pour sélectionner l'une des deux banques de mémoire présentes sur la carte Big Bang.

Mon idée est simplement d'utiliser le signal B1 également en mode normal, pour pouvoir adresser quatre banques au lieu de deux.

Pour faire cela, j'ai utilisé deux commutateurs électroniques, appelés "portes de transmission", connectés comme indiqué ci-dessous.

Lorsque /ML est activé, la sortie d'IC32 est envoyée normalement au DP8421. Le contrôleur DRAM est donc correctement programmé. Lorsque /ML est annulé, la ligne d'adresse A26 est connectée au DP8421. Lorsque la valeur de A26 est 0, les deux banques de mémoire habituelles sont adressées via /RAS0 et /RAS1. Lorsque sa valeur est 1, les deux nouvelles banques de mémoire sont adressées via /RAS2 et /RAS3.

Si vous n'êtes pas familier avec la notation hexadécimale, vous pouvez lire cette petite explication.

Il est important de configurer les deux blocs de mémoire avec des adresses qui diffèrent par le bit 26. Par exemple, les deux banques de mémoire habituelles sont adressées dans la plage $1200000-$19FFFFF (0000 0001 xxxx xxxx xxxx xxxx xxxx xxxx). Les deux nouvelles banques, à la place, sont adressées dans la plage $5200000-$59FFFFF (0000 0101 xxxx xxxx xxxx xxxx xxxx xxxx). Comme vous pouvez le constater, les deux adresses diffèrent par la valeur du bit A26. Par exemple, si vous exécutez la commande "addmem 1200000 19FFFFF" puis "addmem 3200000 39FFFFF" (0000 0011 xxxx xxxx xxxx xxxx xxxx xxxx), vous configurerez deux fois la même banque de mémoire, car les deux adresses ont la même valeur dans le bit A26 !

Vous pouvez choisir d'utiliser une ligne d'adresse différente, puis configurer la mémoire dans différentes plages, mais rappelez-vous que le bit 24 est toujours égal à 1 en mode non AutoConfig. Les autres bits les plus significatifs sont inutilisés. Ainsi, avec mon exemple de connexion, je peux configurer le deuxième bloc de la plage $D200000-$D9FFFFF (0000 1101 xxxx xxxx xxxx xxxx xxxx xxxx).

Réalisation pratique

Les choses dont vous avez besoin pour construire cette extension sont les suivantes :

- Une puce 4066 (portes de transmission).

- Une puce 4049 (portes "NOT").

- Deux barrettes SIMM 8 Mo (EDO ou non) assemblées avec des puces DRAM de 1 Mo. Si vous possédez déjà des puces DRAM ZIP 1Mbx4, vous pouvez les conserver et ajouter 8 ou 12 Mo supplémentaires.

- Un fil fin.

- Vous pouvez éventuellement construire une petite carte avec des emplacements SIMM et ZIP.

Ensuite, vous devez connecter les puces CMOS. Les connexions sont montrées plus haut et résumées dans les tableaux suivants :

| Numéro de broche du 4066 | Connecté à |

| 1 | Pas connecté |

| 2 | Pas connecté |

| 3 | Pas connecté |

| 4 | Pas connecté |

| 5 | Pas connecté |

| 6 | Broche 52 du DP8421 |

| 7 | GND (masse) |

| 8 | A26 du 68030 |

| 9 | Broche 33 du DP8421 |

| 10 | Broche 33 du DP8421 ou simplement connecté à la broche précédente |

| 11 | Broche 16 de l'IC32 |

| 12 | Broche 4 du 4049 |

| 13 | Pas connecté |

| 14 | +5V |

| Numéro de broche du 4049 | Connecté à |

| 1 | +5V |

| 2 | Pas connecté |

| 3 | Pas connecté |

| 4 | Broche 12 du 4066 |

| 5 | Pas connecté |

| 6 | Pas connecté |

| 7 | Pas connecté |

| 8 | GND (masse) |

| 9 | Pas connecté |

| 10 | Pas connecté |

| 11 | Pas connecté |

| 12 | Pas connecté |

| 13 | Pas connecté |

| 14 | Pas connecté |

| 15 | Pas connecté |

| 16 | Pas connecté |

Enfin, j'ai construit un adaptateur SIMM vers ZIP, mais si vous possédez d'autres types de puces mémoire (ZIP, DIP, SIMM 30 broches...), vous pouvez construire votre propre adaptateur. Un adaptateur SIMM vers ZIP peut être construit selon le schéma ci-dessous. Notez que plusieurs broches des deux SIMM peuvent être connectées ensemble, mais certaines ont une connexion exclusive.

Les dénominations M1....M16 se rapportent aux emplacements ZIP de la carte Big Bang. Les dénominations de la Super Big Bang sont différentes. Il semble que les correspondances soient celles contenues dans le tableau suivant :

Correspondance des dénominations des emplacements ZIP

| Dénomination de l'emplacement ZIP de la Big Bang |

Dénomination de l'emplacement ZIP de la Super Big Bang |

| M1 | M1 |

| M2 | M3 |

| M3 | M5 |

| M4 | M7 |

| M5 | M9 |

| M6 | M12 |

| M7 | M13 |

| M8 | M15 |

| M9 | M2 |

| M10 | M4 |

| M11 | M16 |

| M12 | M8 |

| M13 | M10 |

| M14 | M11 |

| M15 | M14 |

| M16 | M16 |

Adaptateur SIMM vers ZIP

| Numéro de la broche SIMM | Numéro sortie SIMM | Connecté à |

| 1 | Les deux | GND (masse), broche 5 de n'importe quel emplacement ZIP |

| 2 | Les deux | D0, broche 6 de l'emplacement ZIP M1 ou M9 |

| 3 | Les deux | D18, broche 6 de l'emplacement ZIP M5 ou M13 |

| 4 | Les deux | D1, broche 7 de l'emplacement ZIP M1 ou M9 |

| 5 | Les deux | D19, broche 7 de l'emplacement ZIP M5 ou M13 |

| 6 | Les deux | D2, broche 3 de l'emplacement ZIP M1 ou M9 |

| 7 | Les deux | D20, broche 3 de l'emplacement ZIP M5 ou M13 |

| 8 | Les deux | D3, broche 4 de l'emplacement ZIP M1 ou M9 |

| 9 | Les deux | D21, broche 4 de l'emplacement ZIP M5 ou M13 |

| 10 | Les deux | +5V, broche 15 de n'importe quel emplacement ZIP |

| 11 | Aucun | Pas connecté |

| 12 | Les deux | A0, broche 11 de n'importe quel emplacement ZIP |

| 13 | Les deux | A1, broche 12 de n'importe quel emplacement ZIP |

| 14 | Les deux | A2, broche 13 de n'importe quel emplacement ZIP |

| 15 | Les deux | A3, broche 14 de n'importe quel emplacement ZIP |

| 16 | Les deux | A4, broche 16 de n'importe quel emplacement ZIP |

| 17 | Les deux | A5, broche 17 de n'importe quel emplacement ZIP |

| 18 | Les deux | A6, broche 18 de n'importe quel emplacement ZIP |

| 19 | Aucun | Pas connecté. Si la barrette SIMM utilise ce signal, elle ne peut pas être adaptée |

| 20 | Les deux | D4, broche 6 de l'emplacement ZIP M2 ou M10 |

| 21 | Les deux | D22, broche 6 de l'emplacement ZIP M6 ou M14 |

| 22 | Les deux | D5, broche 7 de l'emplacement ZIP M2 ou M10 |

| 23 | Les deux | D23, broche 7 de l'emplacement ZIP M6 ou M14 |

| 24 | Les deux | D6, broche 3 de l'emplacement ZIP M2 ou M10 |

| 25 | Les deux | D24, broche 3 de l'emplacement ZIP M6 ou M14 |

| 26 | Les deux | D7, broche 4 de l'emplacement ZIP M2 ou M10 |

| 27 | Les deux | D25, broche 4 de l'emplacement ZIP M6 ou M14 |

| 28 | Les deux | A7, broche 19 de n'importe quel emplacement ZIP |

| 29 | Aucun | Pas connecté |

| 30 | Les deux | +5V, broche 15 de n'importe quel emplacement ZIP |

| 31 | Les deux | A8, broche 20 de n'importe quel emplacement ZIP |

| 32 | Les deux | A9, broche 10 de n'importe quel emplacement ZIP |

| 33 | 1 | /RAS1, broche 39 du DP8421 |

| 33 | 2 | /RAS3, broche 41 du DP8421 |

| 34 | 1 | /RAS0, broche 38 du DP8421 |

| 34 | 2 | /RAS2, broche 40 du DP8421 |

| 35 | Aucun | Pas cobnecté |

| 36 | Aucun | Pas connecté |

| 37 | Aucun | Pas connecté |

| 38 | Aucun | Pas connecté |

| 39 | Les deux | GND (masse), broche 5 de n'importe quel emplacement ZIP |

| 40 | Les deux | /CAS0, broche 2 de l'emplacement ZIP M1, M2, M9 ou M10 |

| 41 | Les deux | /CAS2, broche 5 de l'emplacement ZIP M5, M6, M13 ou M14 |

| 42 | Les deux | /CAS3, broche 5 de l'emplacement ZIP M7, M8, M15 ou M16 |

| 43 | Les deux | /CAS1, broche 5 de l'emplacement ZIP M3, M4, M11 ou M12 |

| 44 | 1 | /RAS0, broche 38 de DP8421 |

| 44 | 2 | /RAS2, broche 40 de DP8421 |

| 45 | 1 | /RAS1, broche 39 de DP8421 |

| 45 | 2 | /RAS3, broche 41 de DP8421 |

| 46 | Aucun | Pas connecté |

| 47 | Les deux | /WE, broche 8 de n'importe quel emplacement ZIP, ou broche 36 de DP8421 |

| 48 | Aucun | Pas connecté |

| 49 | Les deux | D9, broche 6 de l'emplacement ZIP M3 ou M11 |

| 50 | Les deux | D27, broche 6 de l'emplacement ZIP M7 ou M15 |

| 51 | Les deux | D10, broche 7 de l'emplacement ZIP M3 ou M11 |

| 52 | Les deux | D11, broche 7 de l'emplacement ZIP M7 ou M15 |

| 53 | Les deux | D11, broche 3 de l'emplacement ZIP M3 ou M11 |

| 54 | Les deux | D29, broche 3 de l'emplacement ZIP M7 ou M15 |

| 55 | Les deux | D12, broche 4 de l'emplacement ZIP M3 ou M11 |

| 56 | Les deux | D30, broche 4 de l'emplacement ZIP M7 ou M15 |

| 57 | Les deux | D13, broche 6 de l'emplacement ZIP M4 ou M12 |

| 58 | Les deux | D31, broche 6 de l'emplacement ZIP M8 ou M16 |

| 59 | Les deux | +5V, broche 15 de n'importe quel emplacement ZIP |

| 60 | Les deux | D32, broche 7 de l'emplacement ZIP M8 ou M16 |

| 61 | Les deux | D14, broche 7 de l'emplacement ZIP M4 ou M12 |

| 62 | Les deux | D33, broche 3 de l'emplacement ZIP M8 ou M16 |

| 63 | Les deux | D15, broche 3 de l'emplacement ZIP M4 ou M12 |

| 64 | Les deux | D34, broche 4 de l'emplacement ZIP M8 ou M16 |

| 65 | Les deux | D16, broche 4 de l'emplacement ZIP M4 ou M12 |

| 66 | Aucun | Pas connecté |

| 67 | Aucun | Pas connecté |

| 68 | Aucun | Pas connecté |

| 69 | Aucun | Pas connecté |

| 70 | Aucun | Pas connecté |

| 71 | Aucun | Pas connecté |

| 72 | Les deux | GND (masse), broche 5 de n'importe quel emplacement ZIP |

J'ai également connecté une dizaine de condensateurs de dérivation 10 microFarad entre les entrées +5V et GND à proximité des barrettes SIMM, afin d'éviter une chute de tension pendant les transitions. Mais peut-être ne sont-ils pas strictement nécessaires, car il existe déjà des condensateurs de dérivation sur les barrettes SIMM et près des emplacements ZIP.

Vérifiez chaque fois si la connexion n'est pas défectueuse et qu'il n'y a pas de court-circuit !

Vous devez maintenant régler les commutateurs et cavaliers de la carte Big Bang sur 8 Mo de mémoire, en mode non automatique, comme expliqué dans le manuel. Utilisez ensuite la commande "addmem" (fournie avec la carte) pour configurer votre mémoire dans les plages d'adresses appropriées.

Notes finales

Voici mon estimation des coûts de cette bidouille :

- Les deux puces CMOS : 2 $.

- Fil fin : 0,30 $ par mètre.

- Un couple de SIMM 8 Mo : 45 $.

- Un couple d'emplacements SIMM : 10 $.

- Beaucoup de patience, de tests, de brûlures au fer à souder... : remboursé par votre succès !

Salutations à ma compagnie (surtout les filles ;)), aux utilisateurs Amiga à Padoue et à Vérone (en Italie, dans le monde...), à mon ami canadien Rino, à ma famille et à tous ceux qui me connaissent.

Annexe : les circuits logiques alternatifs

Le premier circuit utilise des portes logiques, le second utilise un multiplexeur.

Ces solutions peuvent être plus rapides que celle que j'utilise actuellement, mais je ne les ai pas testées.

Théorie

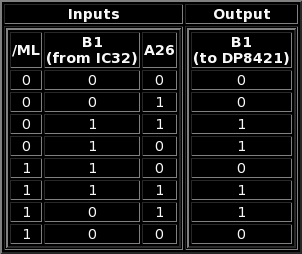

Lorsque /ML=0, la sortie doit être égale à B1. Lorsque /ML=1, le résultat doit être égal à A26. La table de vérité est la suivante :

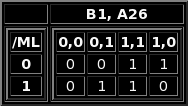

Nous suivons maintenant l'approche standard, basée sur la table de Karnaugh, qui donne un réseau logique à "trois niveaux". Notre table Karnaugh est la suivante :

Il est clair que nous avons besoin d'une porte NOT, de trois portes AND avec deux entrées chacune et d'une porte OR avec trois entrées. La connexion est indiquée ci-dessous.

Comme expliqué par la table de vérité, une autre solution évidente peut être obtenue en utilisant un multiplexeur 2/1, simplement connecté comme indiqué dans le schéma suivant :

Réalisation pratique

Vous pouvez utiliser des puces TTL, éventuellement de la famille logique FAST (codes 74Fxx). Quoi qu'il en soit, votre objectif devrait être de minimiser les délais.

Je ne connais pas le brochage de ces puces, donc je ne peux pas vous expliquer comment établir les véritables connexions.

|